1 STM 32 関連外部インターフェース学習#

1.1 GPIO#

STM 32 F 4 の各グループの汎用 GPIO ポートは、7 つの 32 ビットのレジスタによって制御されます。これには以下が含まれます:

- 4 つの 32 ビット設定レジスタ(MODER、OTYPER、OSPEEDR、PUPDR)

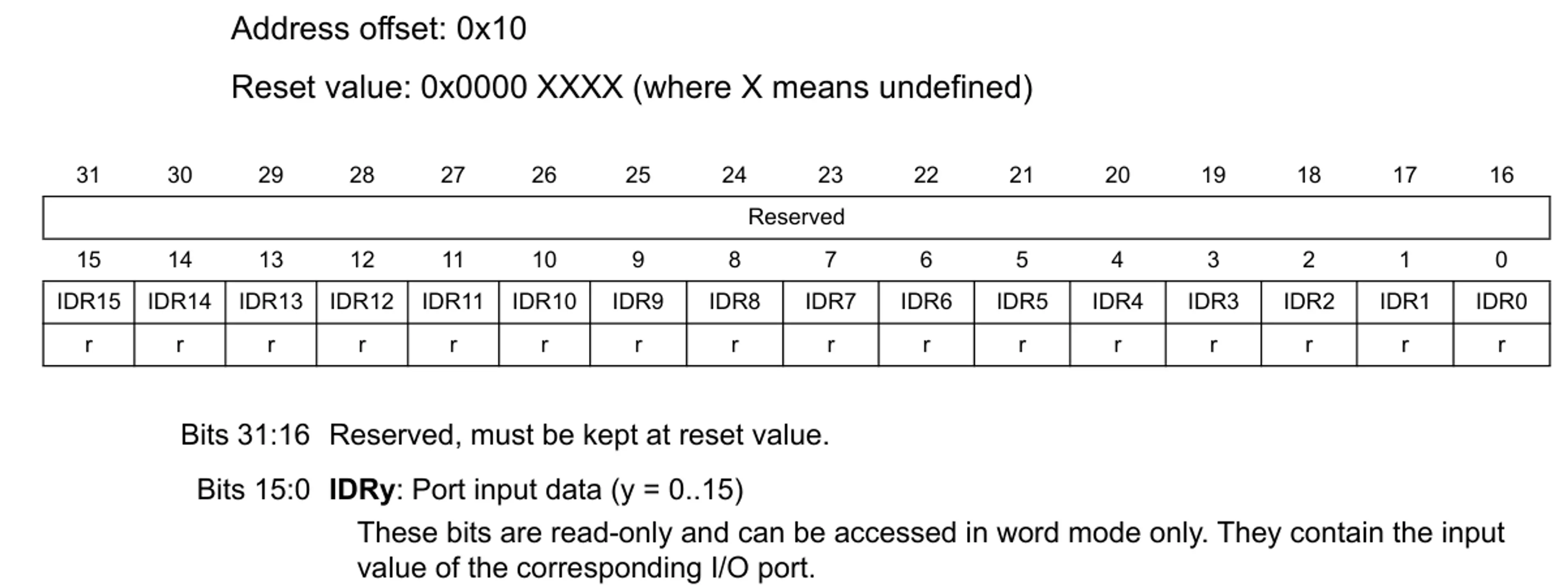

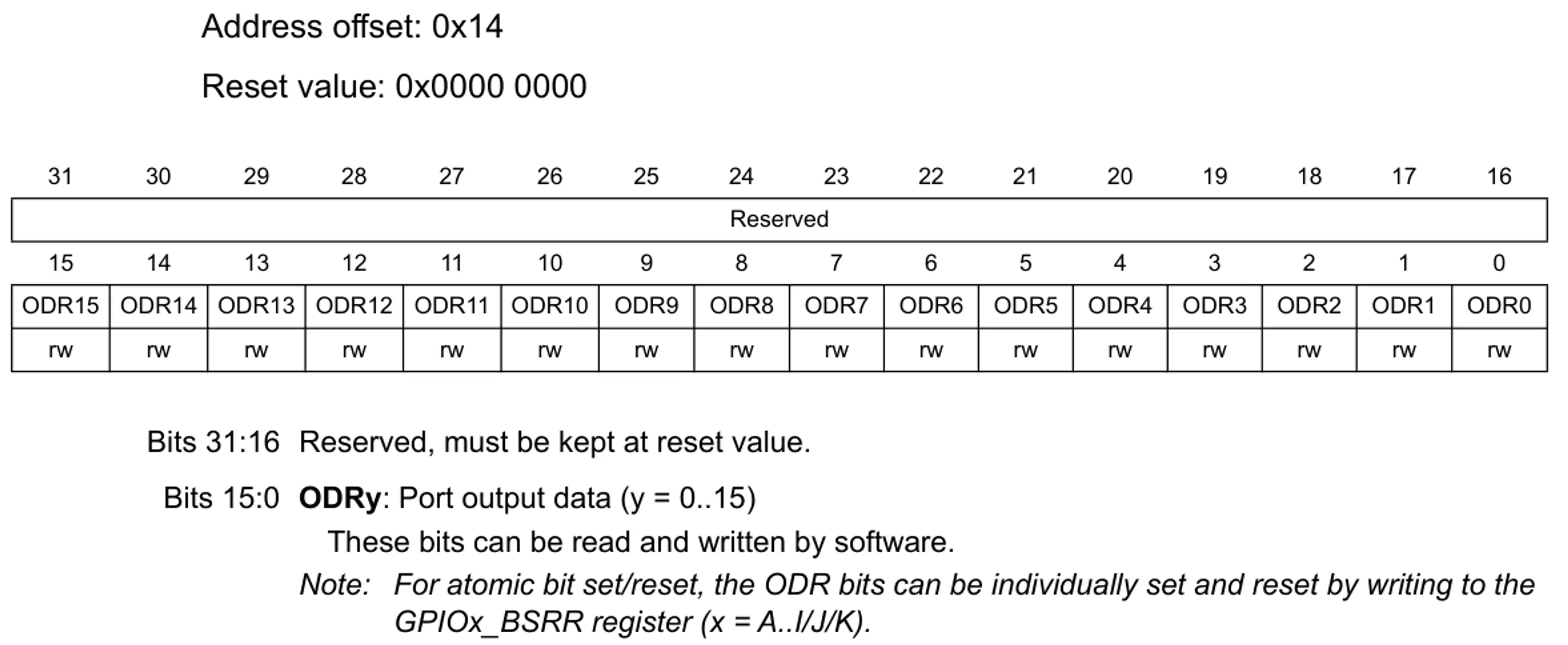

- 2 つの 32 ビットデータレジスタ(IDR、ODR)

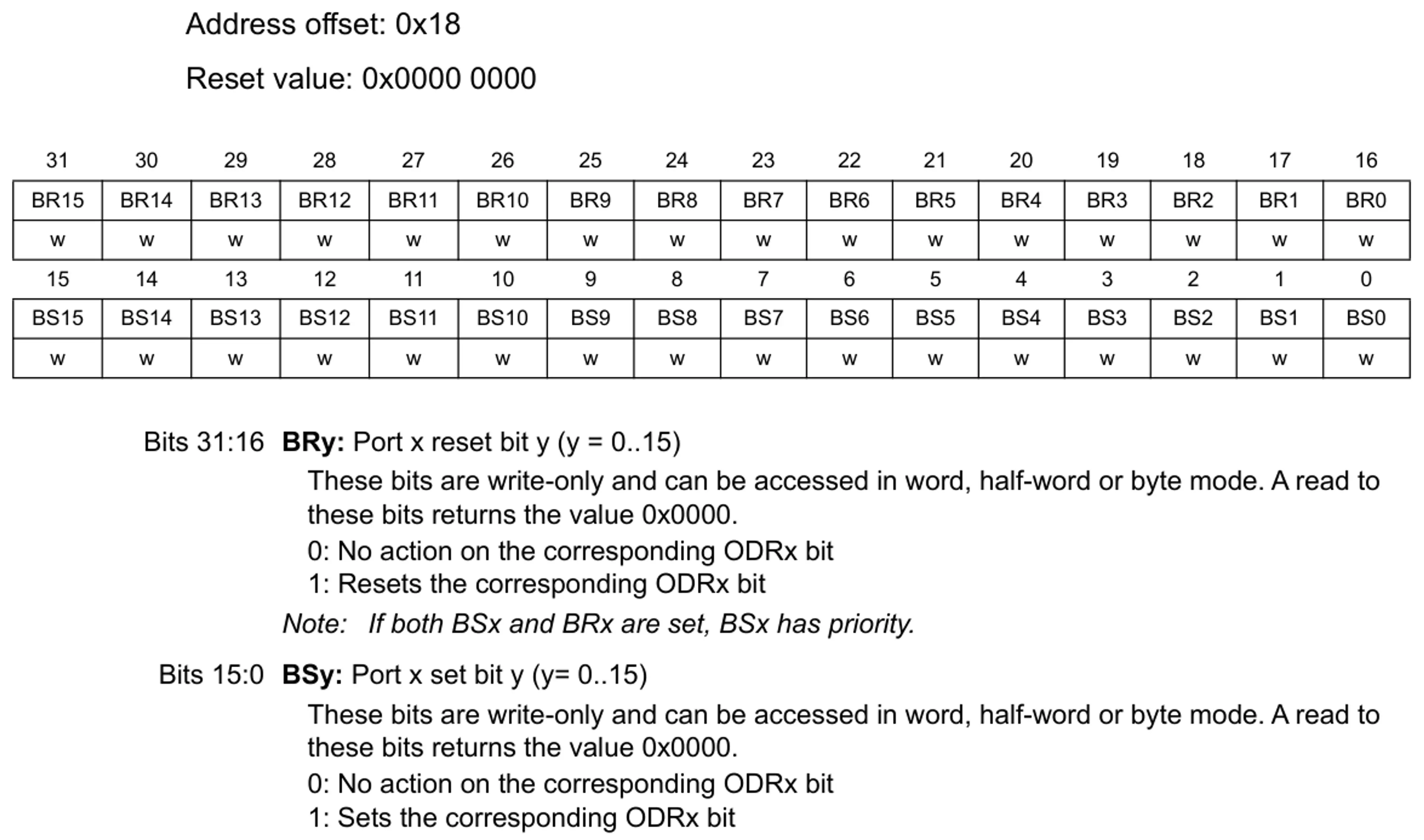

- 1 つの 32 ビットセット、リセットレジスタ(BSRR)

- 1 つの 32 ビットロックレジスタ(LCKR)

- 2 つの 32 ビット多重機能選択レジスタ(AFRH、AFRL)

1.1.1 レジスタ#

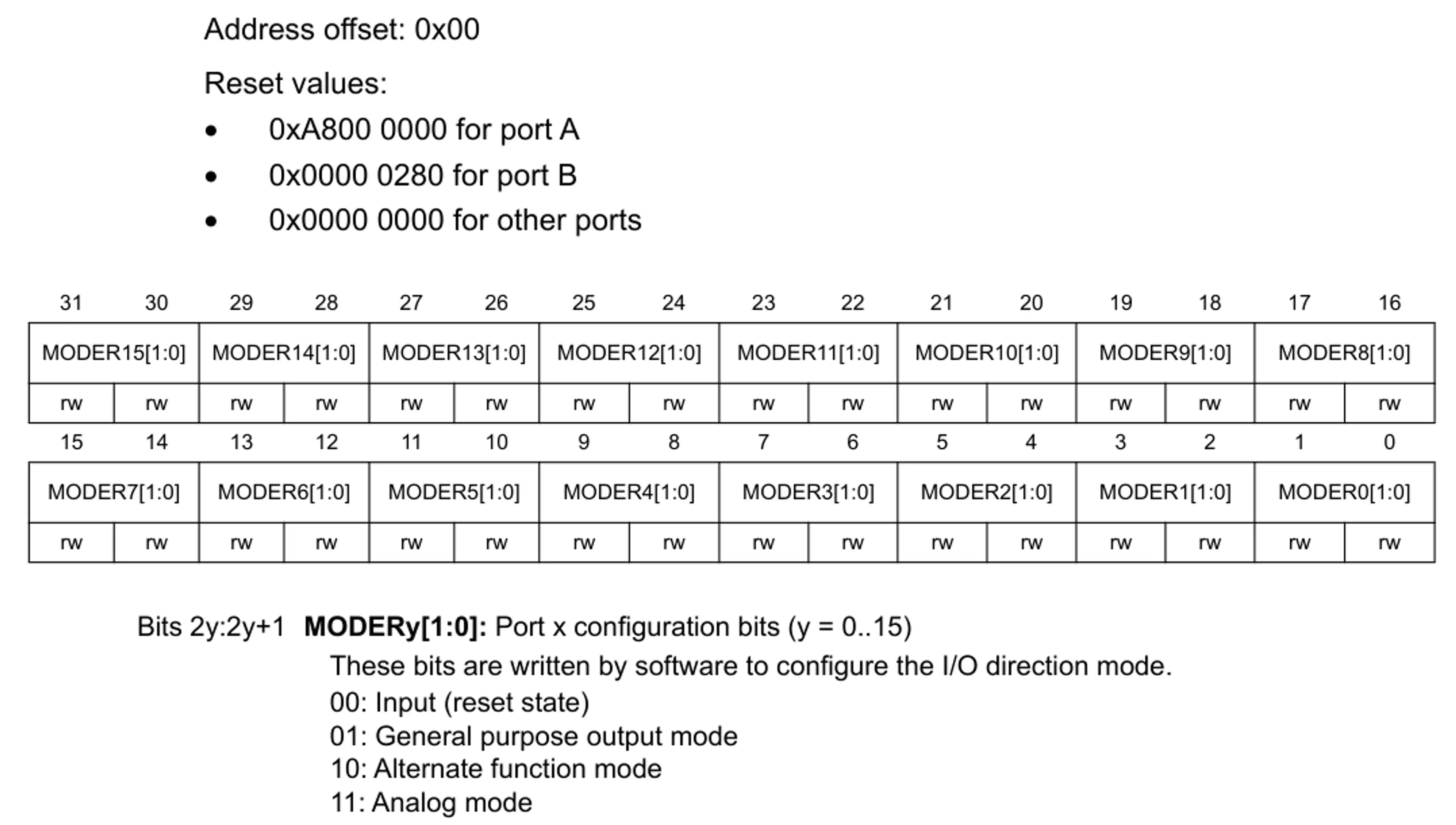

1.1.1.1 GPIO ポートモードレジスタ(GPIOx_MODER)(x=A.. I)#

GPIO の動作モードを制御するために使用されます。

各グループの GPIO には 16 の IO ポートがあり、2 つのレジスタビットが 1 つの IO を制御します。PortA のリセット値は 0 xA 800 0000 で、対応するバイナリは 1010 1000 0000 0000 0000 0000 0000 0000 であり、PA 15/14/13 はすべて多重機能モードであり、残りのポートは入力モードです。

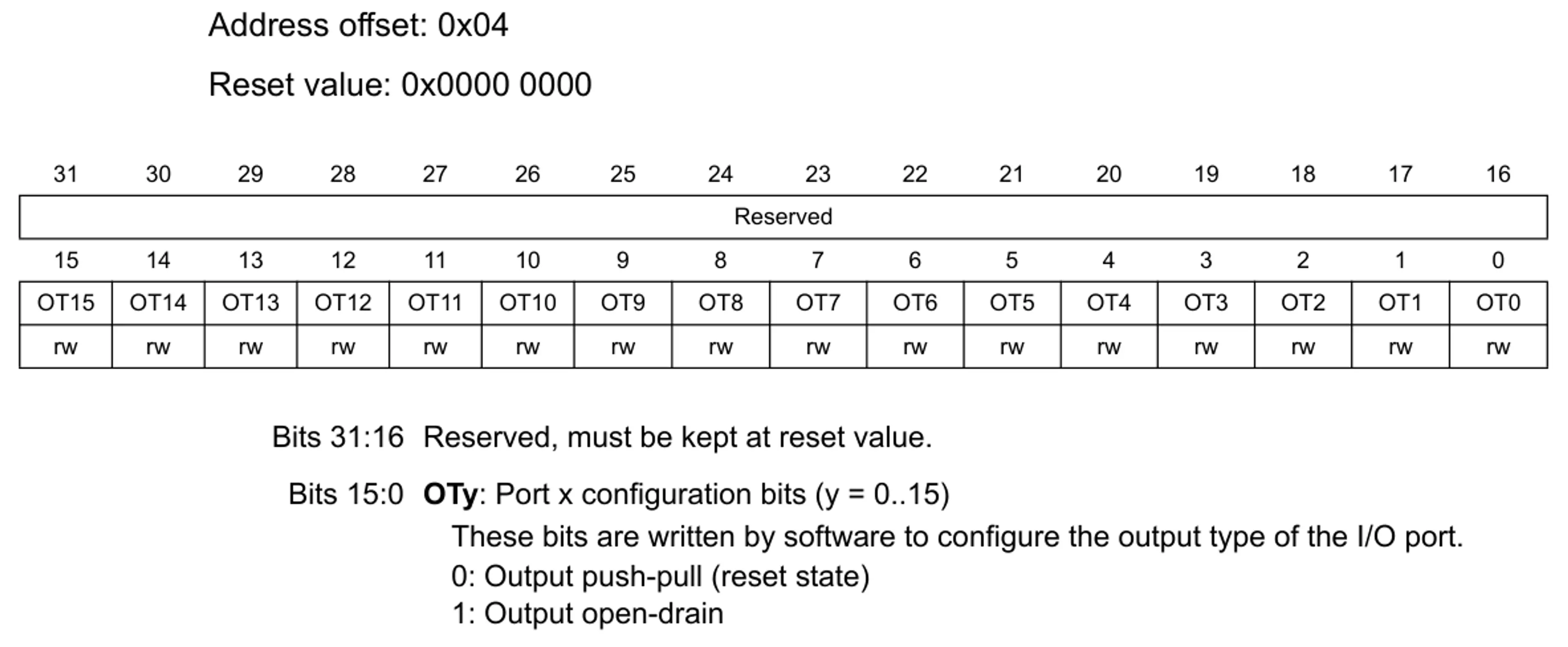

1.1.1.2 GPIO ポート出力タイプコントローラ(GPIOx_OTYPER)#

GPIO の出力タイプを制御するために使用されます。

入力モードでは機能しません。下位 16 ビットが有効です。デフォルトの出力モードでは IO ポートはプッシュプル出力です。

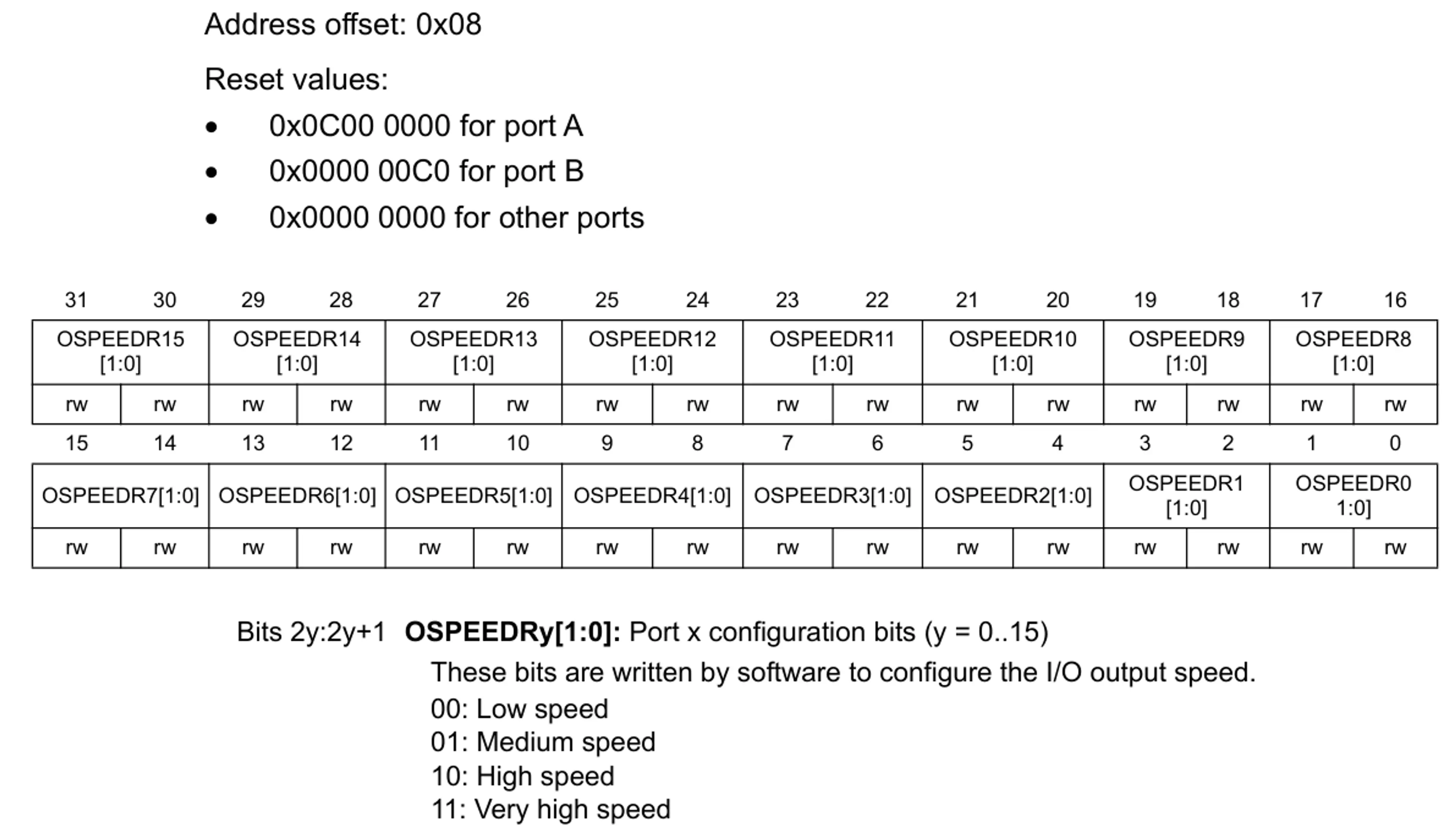

1.1.1.3 GPIO ポート出力速度レジスタ(GPIOx_OSPEEDR)#

出力モードでのみ使用されます。

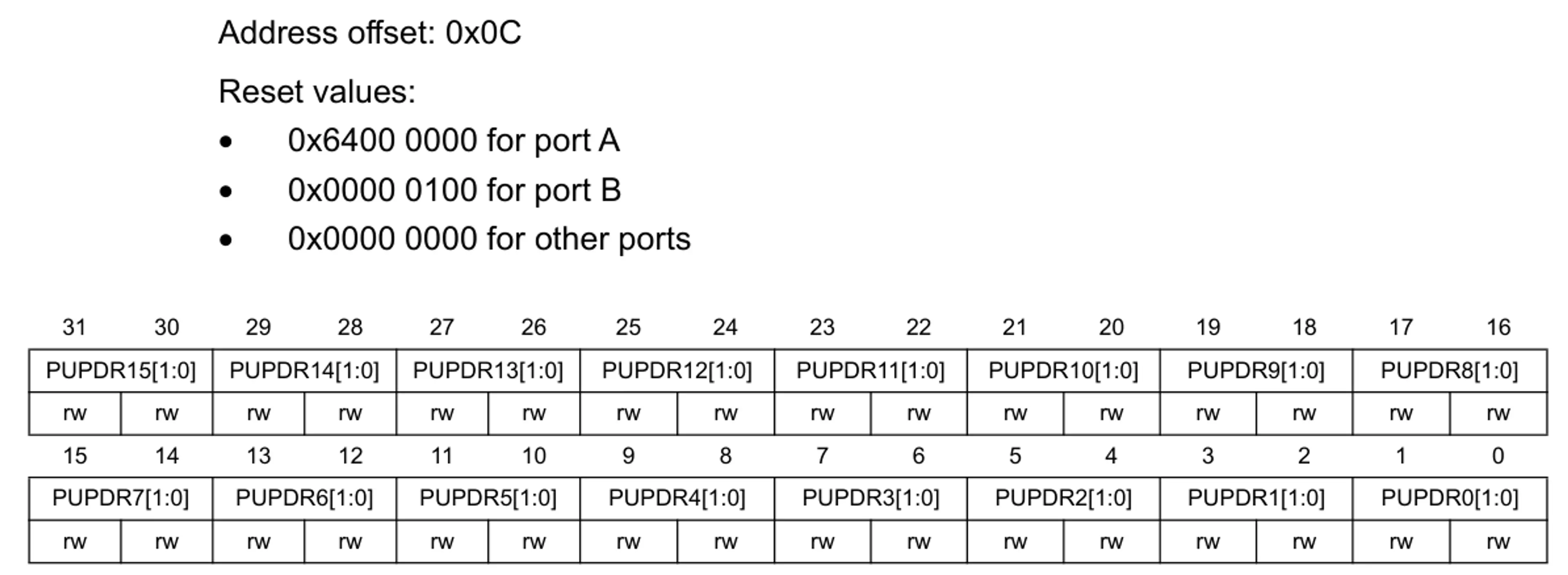

1.1.1.4 GPIO ポートプルアップ / プルダウンレジスタ(GPIOx_PUPDR)#

- 00:プルアップ / プルダウンなし

- 01:プルアップ

- 10:プルダウン

- 11:保持

1.1.1.5 GPIO 入力データレジスタ(GPIOx_IDR)#

1.1.1.6 GPIO 出力データレジスタ(GPIOx_ODR)#

1.1.1.7 GPIO ポートセット / リセットレジスタ(GPIOx_BSRR)#

1.2 ADC#

STM 32 F 4 には、独立して使用できる 3 つの ADC があり、そのうち ADC 1 と ADC 2 はサンプリングレートを向上させるためにデュアルモードを構成できます。STM 32 の ADC は 12 ビット逐次近似型 ADC です。19 のチャネルを含み、16 の外部および 2 の内部信号源および Vbat チャネルの信号を測定できます。これらのチャネルの A/D 変換は、単発、連続、スキャン、不連続サンプリングモードで行うことができます。変換後の結果は、LSB または MSB の 16 ビットデータレジスタに格納されます。

1.2.1 主な特性#

- 設定可能な 12 ビット、10 ビット、8 ビット、6 ビットの解像度

- 変換終了、注入変換終了、アナログウォッチドッグまたはオーバーフローが発生したときに割り込みを生成

- 単発および連続変換モード

- 内蔵データの一貫性を保証するためのデータアライメント

- 各チャネルのサンプリング時間を独立して設定

- 不連続サンプリングモード

- ADC 電源:全速運転時は 2.4 V から 3.6 V、低速運転時は 1.8 V

- ADC 入力範囲:$V_{REF-} \leq V_{IN}\leq V_{REF+}$

- 規則チャネル変換中に DMA リクエストを生成可能

1.2.2 変換順序#

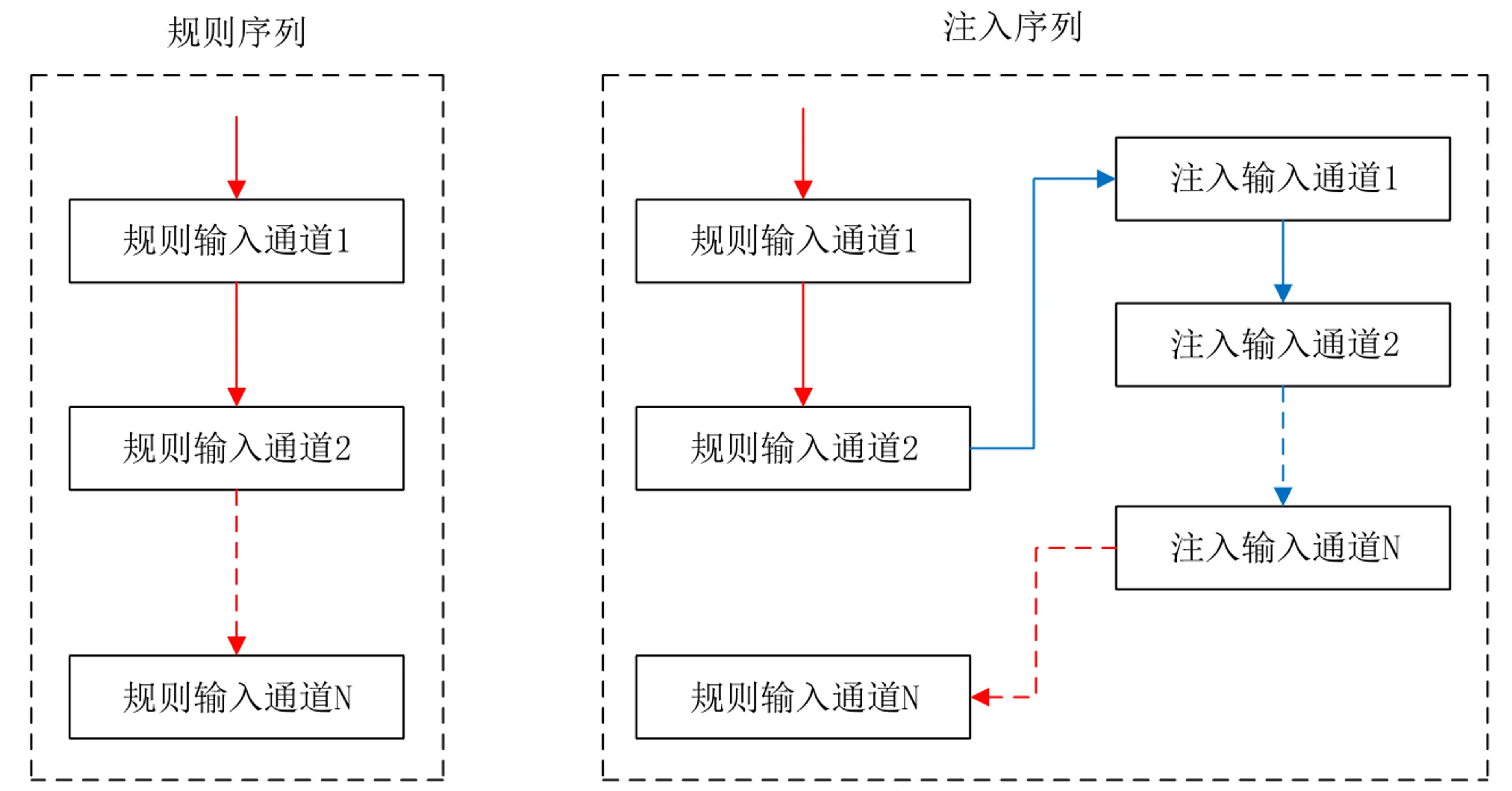

任意の ADCx マルチチャネルが任意の順序で一連の変換を行うと、グループ変換が誕生します。グループ変換には、規則グループと注入グループの 2 種類があります。規則グループは最大 16 の入力チャネルの変換を許可し、注入グループは最大 4 の入力チャネルの変換を許可します。

1.2.2.1 規則グループ#

一定の順序でグループ変換を行います。一般的に使用されます。

1.2.2.2 注入グループ#

「注入」とは元の状態を破ることを意味し、割り込みに相当します。規則グループの変換中に注入グループが起動すると、注入グループの変換が完了した後に規則グループが変換を続けます。

1.2.2.3 変換速度#

ADC 変換時間計算式は $$

T_{CONV}=Sample_Time+TSAR\times ADC_CLK

サンプリング時間は ADC_SMPR レジスタによって制御されます。

ADC_CLK は APB 2 によって生成され、分周係数は RCC_CFGR レジスタの PPRE 2 で設定され、2/4/6/8/16 の分周オプションがあります。

### レジスタ

## Timer

タイマーの基本特性表は以下の通りです:

## SPI

SPI の正式名称は Serial Peripheral interface、シリアル周辺機器インターフェースです。SPI の構造ブロック図は以下の通りです:

SPI のピン情報は次のとおりです。

1. MISO(Master In / Slave Out):マスターデバイスデータ入力、スレーブデバイスデータ出力。

2. MOSI(Master Out / Slave In):マスターデバイスデータ出力、スレーブデバイスデータ入力。

3. SCLK(Serial Clock):クロック信号、マスターデバイス出力。

4. CS(Chip Select):スレーブデバイスチップ選択信号、マスターデバイス出力。

==動作原理==:SPI 通信を行うスレーブとマスターの両方にシフトレジスタがあります。マスターは自身のシフトレジスタに 1 バイトのデータを書き込むことで伝送を開始します。シフトレジスタは MOSI を介してバイトをスレーブに送信し、同時にスレーブはバイトのシフトレジスタの内容を MISO を介してマスターに送信します。これにより、2 つのシフトレジスタ間でデータの交換が実現します。したがって、書き込み操作のみを行う場合、マスターは受信したデータを無視できます。マスターがスレーブのデータを読み取る場合は、空のバイトを送信してスレーブの送信を引き起こします。

SPI はフルデュプレックス、ハーフデュプレックス、シングルデュプレックスの伝送方式をサポートしています。

### SPI 動作モード

SPI の動作モードは CPOL と CPHA によって決定され、どちらも 0 と 1 の 2 つの状態を持つため、SPI には 4 つの動作モードがあります。

| 動作モード | CPOL | CPHA | SCL アイドル状態 | サンプリングエッジ | サンプリング時刻 |

| ---- | ---- | ---- | -------- | ---- | ---- |

| 0 | 0 | 0 | 低電圧 | 上昇エッジ | 奇数エッジ |

| 1 | 0 | 1 | 低電圧 | 下降エッジ | 偶数エッジ |

| 2 | 1 | 0 | 高電圧 | 下降エッジ | 奇数エッジ |

| 3 | 1 | 1 | 高電圧 | 上昇エッジ | 偶数エッジ |

表からわかるように、CPOL は SCL のアイドル状態が高電圧か低電圧かを決定し、CPHA はクロックの奇数エッジでサンプリングするか偶数エッジでサンプリングするかを決定します。

### SPI レジスタ

#### SPI_CR 1(SPI 制御レジスタ 1)

- Bit 11 DFF:データフレーム形式、0:8 ビットデータフレーム、1:16 ビット

- Bit 10 RXONLY:受信のみ。0:フルデュプレックス、1:受信のみ

- Bit 7:フレーム形式。0:MSB を先に送信、1:LSB を先に送信。**通信中にこのビットを変更してはいけません**

- Bit 6:SPI 有効。0:周辺機器をオフ、1:周辺機器を有効。

- Bit 5-3:BR[2:0]:ボーレートを制御します。

-

- Bit 2:マスターモード選択。0:スレーブモード、1:マスターモード

- Bit 1:CPOL

- Bit 0:CPHA

#### SPI_SR(SPI ステータスレジスタ)

- 15-9 ビットは予約されており、強制的に 0 です

- Bit 8:フレーム形式エラー。0:フレーム形式エラーなし、1:フレーム形式エラーあり

- Bit 7:ビジーフラグ。0:ビジー状態でない、1:SPI が通信状態または Tx バッファが空でない

- Bit 1:送信バッファ空。0:空でない、1:空

- Bit 0:受信バッファ空でない。0:空、1:空でない

#### SPI_DR(SPI データレジスタ)

データフレームが 8 ビットの場合は下位 8 ビットのみを使用し、16 ビットの場合はレジスタ全体を使用します。